# Design and Testing Of Prefix Adder for High Speed Application by Using Verilog HDL

<sup>1,</sup> Rajitha Chandragiri, <sup>2,</sup> P. Venkata Lavanya

<sup>1</sup>, Research Scholar, ECE Dept, TKR College of Engineering & Technology, Hyderabad, AP-INDIA

<sup>2</sup>Assoc Prof, ECE Dept, TKR College of Engineering & Technology, Hyderabad, AP-INDIA

# ABSTRACT:

Parallel prefix adder is the most flexible and widely used for binary addition. Parallel Prefix adders are best suited for VLSI implementation. Numbers of parallel prefix adder structures have been proposed over the past years intended to optimize area, fan-out, and logic depth and inter connect count. This paper presents a new approach to redesign the basic operators used in parallel prefix architectures. The number of multiplexers contained in each Slice of an FPGA is considered here for the redesign of the basic operators used in parallel prefix tree. The experimental results indicate that the new approach of basic operators make some of the parallel prefix adder's architectures faster and area efficient.

Keywords: Ripple Carry Adder, Parallel Prefix, Kogge Stone, ASIC, Sparse Adders

## I. INTRODUCTION

Addition is a timing critical operation in today's floating point units. In order to develop faster processing, an end-around carry (EAC) was proposed as a part of fused-multiply-add unit which performs multiplication followed by addition [5]. The proposed EAC adder was also investigated through other pre fix adders in FPGA technology as a complete adder [6]. In this thesis, we propose a 128-bit standalone adder with parallel prefix end around carry logic and conditional sum blocks to improve the critical path delay and provide flexibility to design with different adder architectures. In previous works, CLA logic was used for EAC logic. Using a modified structure of a parallel prefix 2n + 1 adder provides flexibility to the design and decreases the length of the carry path. After the architecture is tested and verified, critical path is analyzed using FreePDK45nm library. Full custom design techniques are applied carefully during critical path optimization. Critical path analysis provides fast comparison of the total delay among different architectures without designing the whole circuit and a simpler approach to size the transistors for lowest delay possible. As a final step, datapath is designed as a recurring bitslice for fast layout entry. The results show that the proposed adder shows 142ps delay, 2.42mW average power dissipation, and 3,132 sq. micron area assuming there is not much routing area overhead in the estimated area.

Binary addition is the most fundamental and frequently used arithmetic operation. A lot of work on adder design has been done so far and much architecture have been proposed. When high operation speed is required, tree structures like parallel-prefix adders are used [1] - [10]. In [1], Sklansky proposed one of the earliest tree-prefix is used to compute intermediate signals. In the Brent-Kung approach [2], designed the computation graph for area-optimization. The KS architecture [3] is optimized for timing. The LF architecture [4], is proposed, where the fan-out of gates increased with the depth of the prefix computation tree. The HC adder architecture [5], is based on BK and KS is proposed. In [6], an algorithm for back-end design is proposed. The area minimization is done by using bitwise timing constraints [7]. In [8], which is targeted to minimize the total switching activities under bitwise timing constraints. The architecture [9], saves one logic level implementation and reduces the fan-out requirements of the design. A fast characterization process for Knowles adders is proposed using matrix representation [10]. The Parallel Prefix addition is done in three steps.

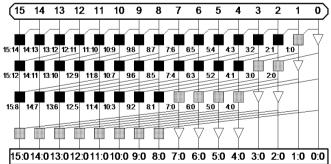

which is shown in fig1. The fundamental generate and propagate signals are used to generate the carry input for each adder. Two different operators black and gray are used here. The aim of this paper is to propose a new approach for the basic operators and make use of these operators in various parallel prefix adders to evaluate their performance with newly redesigned operators. The rest of the paper is organized as follows: In section II, some background information about Parallel Prefix architecture is given. New design approach of

basic operators is discussed in section III. Experimental results are presented in section IV. Conclusions are drawn in section V.

Several papers have attacked the problem of designing efficient diminished adders. The majority of them rely on the use of an inverted end around carry (IEAC) n-bit adder, which is an adder that accepts two nbit operands and provides a sum increased by one compared to their integer sum if their integer addition does not result in a carry output. Although an IEAC adder can be implemented by using an integer adder in which its carry output is connected back to its carry input via an inverter, such a direct feedback is not a good solution. Since the carry output depends on the carry input, a direct connection between them forms a combinational loop that may lead to an unwanted race condition [21]. To this end, a number of custom solutions have been proposed for the design of efficient IEAC adders. Considering the diminished-1 representation for modulo 2n b 1 addition, [4], [5] used an IEAC adder which is based on an integer adder along with an extra carry lookahead (CLA) unit. The CLA unit computes the carry output which is then inverted used as the carry input of the integer adder. Solutions that rely on a single carry computation unit have also been proposed. Zimmermann [22], [23] proposed IEAC adders that make use of a parallel-prefix carry computation unit along with an extra prefix level that handles the inverted end-around carry.

Although these architectures are faster than the carry lookahead ones proposed in [24], for sufficiently wide operands, they are slower than the corresponding parallel prefix integer adders because of the need for the extra prefix level. In [24], it has been shown that the recirculation of the inverted end around carry can be performed within the existing prefix levels, that is, in parallel with the carries' computation. In this way, the need of the extra prefix level is canceled and parallel-prefix IEAC adders are derived that can operate as fast as their integer counterparts, that is, they offer a logic depth of log2 n prefix levels. Unfortunately, this level of performance requires significantly more area than the solutions of [22], [23], since a double parallel-prefix computation tree is required in several levels of the carry computation unit. For reducing the area complexity of the parallel-prefix solutions, select-prefix [25] and circular carry select [26] IEAC adders have been proposed. Unfortunately, both these proposals achieve a smaller operating speed than the parallel-prefix ones of [24]. Recently, very fast IEAC adders that use the Ling carry formulation of parallel-prefix addition [27] have appeared in [28], that also suffer from the requirement of a double parallel-prefix computation tree. Although a modulo 2n b 1 adder that follows the on b 1P-bit weighted representation can be designed following the principles of generic modulo adder design [29], specialized architectures for it have appeared in [30], [31]. However, it has been recently shown [32] that a weighted adder can be designed efficiently by using an IEAC one and a carry save adder (CSA) stage. As a result, improving the design for an IEAC adder would improve the weighted adder design as well.

### **III.PARALLEL-PREFIX ADDITION BASICS**

The binary adder is the critical element in most digital circuit designs including digital signal processors (DSP) and microprocessor datapath units. As such, extensive research continues to be focused on improving the power delay performance of the adder. In VLSI implementations, parallel-prefix adders are known to have the best performance. Reconfigurable logic such as Field Programmable Gate Arrays (FPGAs) has been gaining in popularity in recent years because it offers improved performance in terms of speed and power over DSP-based and microprocessor-based solutions for many practical designs involving mobile DSP and telecommunications applications and a significant reduction in development time and cost over Application Specific Integrated Circuit (ASIC) designs. The power advantage is especially important with the growing popularity of mobile and portable electronics, which make extensive use of DSP functions. However, because of the structure of the configurable logic and routing resources in FPGAs, parallel-prefix adders will have a different performance than VLSI implementations.

In particular, most modern FPGAs employ a fast-carry chain which optimizes the carry path for the simple Ripple Carry Adder (RCA). In this paper, the practical issues involved in designing and implementing tree-based adders on FPGAs are. An efficient testing strategy for evaluating the performance of these adders is discussed. Several tree-based adder structures are implemented and characterized on a FPGA and compared with the Ripple Carry Adder (RCA) and the Carry Skip Adder (CSA). Finally, some conclusions and suggestions for improving FPGA designs to enable better tree-based adder performance are given.

#### **IV. CARRY-TREE ADDER DESIGNS**

Parallel-prefix adders, also known as carry-tree adders, pre-compute the propagate and generate signals [1]. These signals are variously combined using the fundamental carry operator (fco) [2].

$(gL, pL) \circ (gR, pR) = (gL + pL \cdot gR, pL \cdot pR) (1)$

Due to associative property of the fco, these operators can be combined in different ways to form various adder structures. For, example the four-bit carry-lookahead generator is given by:

c4 = (g4, p4) o [(g3, p3) o [(g2, p2) o (g1, p1)]] (2)

A simple rearrangement of the order of operations allows parallel operation, resulting in a more efficient tree structure for this four bit example:

$c4 = [(g4, p4) \circ (g3, p3)] \circ [(g2, p2) \circ (g1, p1)] (3)$

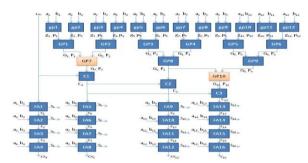

It is readily apparent that a key advantage of the tree structured adder is that the critical path due to the carry delay is on the order of log2N for an N-bit wide adder. The arrangement of the prefix network gives rise to various families of adders. For a discussion of the various carry-treestructures, see [1, 3]. For this study, the focus is on the Kogge-Stone adder [4], known for having minimal logic depth and fanout (see Fig 1(a)). Here we designate BC as the black cell which generates the ordered pair in equation (1); the gray cell (GC) generates the left signal only, following [1]. The interconnect area is known to be high, but for an FPGA with large routing overhead to begin with, this is not as important as in a VLSI implementation. The regularity of the Kogge-Stone prefix network has built in redundancy which has implications for fault-tolerant designs [5]. The sparse Kogge-Stone adder, shown in Fig 1(b), is also studied. This hybrid design completes the summation process with a 4 bit RCA allowing the carry prefix network to be simplified. Another carry-tree adder known as the spanning tree carry-lookahead (CLA) adder is also examined [6]. Like the sparse Kogge-Stone adder, this design terminates with a 4- bit RCA. As the FPGA uses a fast carry-chain for the RCA, it is interesting to compare the performance of this adder with the sparse Kogge-Stone and regular Kogge-Stone adders. Also of interest for the spanning-tree CLA is its testability features [7].

#### V. RELATED WORK

Xing and Yu noted that delay models and cost analysis for adder designs developed for VLSI technology do not map directly to FPGA designs [8]. They compared the design of the ripple carry adder with the carry-lookahead, carry-skip, and carry-select adders on the Xilinx 4000 series FPGAs. Only an optimized form of the carry-skip adder performed better than the ripple carry adder when the adder operands were above 56 bits. A study of adders implemented on the Xilinx Virtex II yielded similar results [9]. In [10], the authors considered several parallel prefix adders implemented on a Xilinx Virtex 5 FPGA. It is found that the simple RCA adder is superior to the parallel prefix designs because the RCA can take advantage of the fast carry chain on the FPGA.Kogge-Stone The Kogge-Stone tree [22] Figure 1.5 achieves both log2N stages and fan-out of 2 at each stage. This comes at the cost of long wires that must be routed between stages. The tree also contains more PG cells; while this may not impact the area if the adder layout is on a regular grid, it will increase power consumption. Despite these cost, Kogge-Stone adder is generally used for wide adders because it shows the lowest delay among other structures.

Another carry-tree adder known as the spanning tree carry-lookahead (CLA) adder is also examined [6]. Like the sparse Kogge-Stone adder, this design terminates with a 4-bit RCA. As the FPGA uses a fast carry-chain for the RCA, it is interesting to compare the performance of this adder with the sparse Kogge-Stone and regular Kogge-Stone adders. Also of interest for the spanning-tree CLA is its testability features [7].

This study focuses on carry-tree adders implemented on a Xilinx Spartan 3E FPGA. The distinctive contributions of this paper are two-fold. First, we consider tree-based adders and a hybrid form which combines a tree structure with a ripple-carry design. The Kogge-Stone adder is chosen as a representative of the former type and the sparse Kogge Stone and spanning tree adder are representative of the latter category. Second, this paper considers the practical issues involved in testing the adders and provides actual measurement data to compare with simulation results

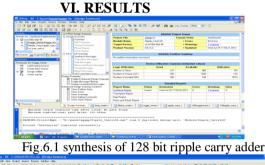

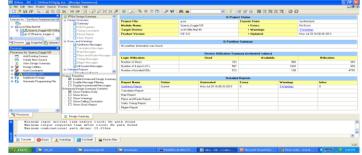

Fig.6.2 synthesis of 128 bit kogge stone adder

Fig.6.2 synthesis of 128 bit sparse-kogge adder

## VII. CONCLUSIONS

This paper presents a new approach for the basic operators of parallel prefix tree adders. In KS, Sparse Kogge delay is reduced by this new approach, The same can be understood with reference to number of logic levels of implementation, as the logic levels are more delay increases. The area requirement can be considered from the utilization of LUTs, Slices and over all gate count. KS and Knowles adders occupies more area in new approach.

| Issn  | 225 | 0-30 | DO5 I |   |

|-------|-----|------|-------|---|

| 10011 |     | 0-50 | 100   | L |

The KS adders are proven even faster than Skalansky adder but they occupy large area compared to Skalansky adder. Finally it can be concluded that the new approach for the redesign of basic operators will speed up the addition process of parallel prefix addition with some area overhead. The performance of these adders can be estimated for high bit-widths. This can be further used in Cryptographic applications, where the addition of more number of bits is necessary. The new approach for the parallel prefix adders can also be used to speed up the addition process in FIR filter and arithmetic operations like multipliers, etc.

#### REFERENCES

- [1] Kogge P, Stone H, "A parallel algorithm for the efficient solution of a general class Computers, vol.C-22, No.8, pp 786-793, Aug.1973. Recurrence relations", IEEE Trans.

- [2] Brent R, Kung H, "A regular layout for parallel adders". IEEE Trans, computers, Vol.C-31, no.3, pp 260-264, March1982.

[3] R. P. Brent and H. T. Kung, "A regular layout for parallel adders," IEEE Trans. Computers, vol. 31, no. 3, pp. 260–264, vol. 31, no. 30, pp. 260–264, vol. 31, no. 31, no. 31, pp. 260–264, vol. 31, no. 3

- March 1982.

[4] P. M. Kogge and H. S. Stone, "A parallel algorithm for the efficient solution of a general class of recurrence equations," IEEE Trans Computers vol 22, no 8 pp. 786–793 August 1973

IEEE Trans. Computers, vol. 22, no. 8, pp. 786–793, August 1973.[5] J. Sklansky, "Conditional sum addition logic," IRE Trans. Electron. Compute., vol. 9, no. 6, pp. 226–231, 1960.

- [6] J. Liu, S. Zhou, H. Zhu, and C.-K. Cheng, "An algorithmic approach for generic parallel adders," in ICCAD, November 2003, pp. 734–730.

- [7] R. Zimmermann, "Non-heuristic optimization and synthesis of parallel-prefix adders," in International Workshop on Logic and Architecture Synthesis, December 1996, pp. 123–132.

- [8] T. Matsunaga and Y. Matsunaga, "Timing-constrained area minimization algorithm for parallel prefix adders," IEICE Transactions on Fundamentals, vol. E90-A, no. 12, pp. 2770– 2777, December 2007.

- [9] T. Matsunaga, S. Kimura, and Y. Matsunaga, "Power-conscious syntheses of parallel prefix adders under bitwise timing constraints," in Proc. the Workshop on Synthesis And System Integration of Mixed Information technologies(SASIMI), Sapporo, Japan, October 2007, pp. 7–14.